### **General Description**

The MAX8794 DDR linear regulator sources and sinks up to 3A peak (typ) using internal n-channel MOSFETs. This linear regulator delivers an accurate 0.5V to 1.5V output from a low-voltage power input ( $V_{\rm IN} = 1.1V$  to 3.6V). The MAX8794 uses a separate 3.3V bias supply to power the control circuitry and drive the internal n-channel MOSFETs.

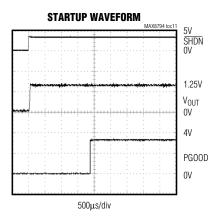

The MAX8794 provides current and thermal limits to prevent damage to the linear regulator. Additionally, the MAX8794 generates a power-good (PGOOD) signal to indicate that the output is in regulation. During startup, PGOOD remains low until the output is in regulation for 2ms (typ). The internal soft-start limits the input surge current.

The MAX8794 powers the active-DDR termination bus that requires a tracking input reference. The MAX8794 can also be used in low-power chipsets and graphics processor cores that require dynamically adjustable output voltages. The MAX8794 is available in a 10-pin, 3mm x 3mm, TDFN package.

### **Applications**

Notebook/Desktop Computers

DDR Memory Termination

Active Termination Buses

Graphics Processor Core Supplies

Chipset/RAM Supplies as Low as 0.5V

#### **Features**

- ♦ Internal Power MOSFETs with Current Limit (3A typ)

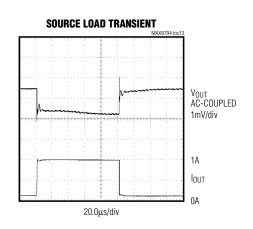

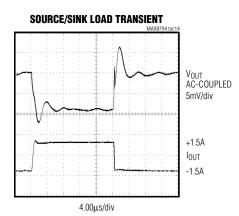

- ♦ Fast Load-Transient Response

- External Reference Input with Reference Output Buffer

- ♦ 1.1V to 3.6V Power Input

- ♦ ±15mV (max) Load-Regulation Error

- **♦ Thermal-Fault Protection**

- **♦** Shutdown Input

- Power-Good Window Comparator with 2ms (typ)

Delay

- ♦ Small, Low-Profile, 10-Pin, 3mm x 3mm TDFN Package

- **♦** Ceramic or Polymer Output Capacitors

### Ordering Information

| PART        | <br>PIN-<br>PACKAGE        | TOP<br>MARK | PKG<br>CODE |

|-------------|----------------------------|-------------|-------------|

| MAX8794ETB+ | <br>10 TDFN<br>(3mm x 3mm) | ABD         | T1033-1     |

<sup>+</sup>Denotes lead-free package.

## Pin Configuration

### TOP VIEW REFOUT 10 OUT $V_{CC}$ :8 PGND AGND MAX8794 SHDN REFIN 6 PG00D **OUTS TDFN** 3mm x 3mm

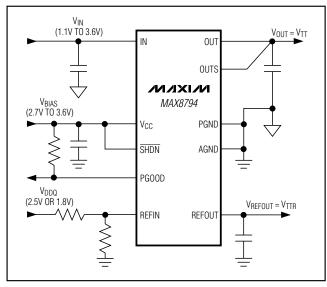

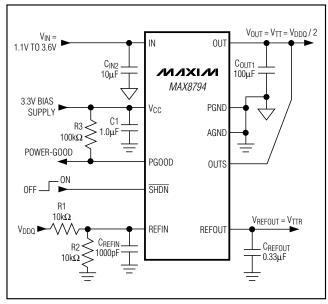

## Typical Operating Circuit

Maxim Integrated Products

### **ABSOLUTE MAXIMUM RATINGS**

| IN to PGND                         | 0.3V to +4.3V                    | Continuous Power Dissipation ( $T_A = +70$ °C) |                |

|------------------------------------|----------------------------------|------------------------------------------------|----------------|

| OUT to PGND                        | 0.3V to $(V_{IN} + 0.3V)$        | 10-Pin 3mm x 3mm TDFN                          |                |

| OUTS to AGND                       | 0.3V to $(V_{IN} + 0.3V)$        | (derated 24.4mW/°C above +70°C)                | 1951mW         |

| V <sub>CC</sub> to AGND            | 0.3V to +4.3V                    | Operating Temperature Range                    |                |

| REFIN, REFOUT, SHDN, PGOOD to AGND | 0.3V to (V <sub>CC</sub> + 0.3V) | MAX8794ETB                                     | 40°C to +85°C  |

| PGND to AGND                       | 0.3V to +0.3V                    | Junction Temperature                           | +150°C         |

| REFOUT Short Circuit to AGND       | Continuous                       | Storage Temperature Range                      | 65°C to +150°C |

| OUT Continuous RMS Current         |                                  | Lead Temperature (soldering, 10s)              | +300°C         |

| 100s                               | ±1.6A                            |                                                |                |

| 19                                 | +2 5A                            |                                                |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{IN}=1.8V,\,V_{CC}=3.3V,\,V_{REFIN}=V_{OUTS}=1.25V,\,\overline{SHDN}=V_{CC},\,circuit\,of\,Figure\,1,\,T_{A}=-40^{\circ}C\,\,to\,\,+85^{\circ}C,\,unless\,otherwise\,noted.$  Typical values are at T\_A = +25^{\circ}C.) (Note 1)

| PARAMETER                                   | SYMBOL          | CON                                                       | IDITIONS                                      | MIN | TYP  | MAX   | UNITS |

|---------------------------------------------|-----------------|-----------------------------------------------------------|-----------------------------------------------|-----|------|-------|-------|

| Innut Valtage Denge                         | VIN             | Power input                                               |                                               | 1.1 |      | 3.6   | V     |

| Input Voltage Range                         | Vcc             | Bias supply                                               |                                               | 2.7 |      | 3.6   |       |

| Quiescent Supply Current (V <sub>CC</sub> ) | Icc             | Load = 0, V <sub>REFIN</sub> >                            | 0.45V                                         |     | 0.7  | 1.3   | mA    |

| Chutdown Cupply Current (Vac)               | lo e (e) (E) () | SHDN = GND, VREF                                          |                                               | 350 | 600  | μA    |       |

| Shutdown Supply Current (V <sub>CC</sub> )  | ICC(SHDN)       | SHDN = GND, REFIN = GND                                   |                                               |     | 50   |       | 100   |

| Quiescent Supply Current (VIN)              | I <sub>IN</sub> | Load = 0                                                  |                                               |     | 0.4  | 10    | mA    |

| Shutdown Supply Current (V <sub>IN</sub> )  | IN(SHDN)        | SHDN = GND                                                |                                               |     | 0.1  | 10    | μΑ    |

| Foodback Voltage Error                      | Va. 170         | REFIN to OUTS,                                            | T <sub>A</sub> = +25°C                        | -4  | 0    | +4    | \/    |

| Feedback-Voltage Error                      | Vouts           | $I_{OUT} = \pm 200 \text{mA}$                             | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ | -6  |      | +6    | mV    |

| Load-Regulation Error                       |                 | -1A ≤ I <sub>OUT</sub> ≤ +1A                              |                                               | -15 |      | +15   | mV    |

| Line-Regulation Error                       |                 | $1.4V \le V_{IN} \le 3.3V$ , Ic                           | OUT = ±100mA                                  |     | 1    |       | mV    |

| OUTS Input Bias Current                     | louts           |                                                           |                                               | -1  |      | +1    | μΑ    |

| OUTPUT                                      |                 |                                                           |                                               |     |      |       |       |

| Output Adjust Range                         |                 |                                                           |                                               | 0.5 |      | 1.5   | V     |

| OLIT On Desigtance                          |                 | High-side MOSFET (source) (I <sub>OUT</sub> = 0.1A)       |                                               |     | 0.10 | 0.169 |       |

| OUT On-Resistance                           |                 | Low-side MOSFET (                                         | $sink) (I_{OUT} = -0.1A)$                     |     | 0.10 | 0.20  | Ω     |

| Output Current Slew Rate                    |                 | Cout = 100µF, lour                                        | r = 0.1A  to  2A                              |     | 3    |       | A/µs  |

| OUT Power-Supply Rejection Ratio            | PSRR            | $10Hz < f < 10kHz, I_{OUT} = 200mA,$ $C_{OUT} = 100\mu F$ |                                               |     | 80   |       | dB    |

| OUT to OUTS Resistance                      | Routs           |                                                           |                                               |     | 12   |       | kΩ    |

| Discharge MOSFET On-<br>Resistance          | RDISCHARGE      | SHDN = GND                                                |                                               |     | 8    |       | Ω     |

## **ELECTRICAL CHARACTERISTICS (continued)**

( $V_{IN}$  = 1.8V,  $V_{CC}$  = 3.3V,  $V_{REFIN}$  =  $V_{OUTS}$  = 1.25V,  $\overline{SHDN}$  =  $V_{CC}$ , circuit of Figure 1,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 1)

| PARAMETER                                         | SYMBOL              | CONDITIONS                                                             | MIN                          | TYP    | MAX                          | UNITS |

|---------------------------------------------------|---------------------|------------------------------------------------------------------------|------------------------------|--------|------------------------------|-------|

| REFERENCE                                         |                     |                                                                        |                              |        |                              |       |

| REFIN Voltage Range                               | VREFIN              |                                                                        | 0.5                          |        | 1.5                          | V     |

| REFIN Input Bias Current                          | IREFIN              |                                                                        | -1                           |        | +1                           | μΑ    |

| REFIN Undervoltage-Lockout<br>Voltage             |                     | Rising edge, hysteresis = 75mV                                         |                              | 0.35   | 0.45                         | V     |

| REFOUT Voltage                                    | V <sub>REFOUT</sub> | V <sub>CC</sub> = 3.3V, I <sub>REFOUT</sub> = 0                        | V <sub>REFIN</sub><br>- 0.01 | VREFIN | V <sub>REFIN</sub><br>+ 0.01 | V     |

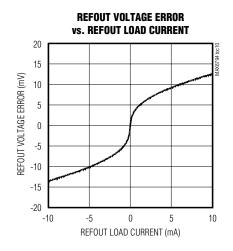

| REFOUT Load Regulation                            | $\Delta V_REFOUT$   | IREFOUT = ±5mA                                                         | -20                          |        | +20                          | mV    |

| FAULT DETECTION                                   |                     |                                                                        |                              |        |                              |       |

| Thermal-Shutdown Threshold                        | T <sub>SHDN</sub>   | Rising edge, hysteresis = 15°C                                         |                              | +165   |                              | °C    |

| V <sub>CC</sub> Undervoltage-Lockout<br>Threshold | V <sub>UVLO</sub>   | Rising edge, hysteresis = 100mV                                        | 2.45                         | 2.55   | 2.65                         | V     |

| IN Undervoltage-Lockout<br>Threshold              |                     | Rising edge, hysteresis = 55mV                                         |                              | 0.9    | 1.1                          | V     |

| Current-Limit Threshold                           | I <sub>LIMIT</sub>  |                                                                        | 1.8                          | 3      | 4.2                          | А     |

| Soft-Start Current-Limit Time                     | tss                 |                                                                        |                              | 200    |                              | μs    |

| INPUTS AND OUTPUTS                                |                     |                                                                        |                              |        |                              |       |

| PGOOD Lower Trip Threshold                        |                     | With respect to feedback threshold, hysteresis = 12mV                  | -200                         | -150   | -100                         | mV    |

| PGOOD Upper Trip Threshold                        |                     | With respect to feedback threshold, hysteresis = 12mV                  | 100                          | 150    | 200                          | mV    |

| PGOOD Propagation Delay                           | tpgood              | OUTS forced 25mV beyond PGOOD trip threshold                           | 5                            | 10     | 35                           | μs    |

| PGOOD Startup Delay                               |                     | Startup rising edge, OUTS within ±100mV of the feedback threshold      |                              | 2      | 3.5                          | ms    |

| PGOOD Output Low Voltage                          |                     | I <sub>SINK</sub> = 4mA                                                |                              |        | 0.3                          | V     |

| PGOOD Leakage Current                             | IPGOOD              | OUTS = REFIN (PGOOD high impedance),<br>PGOOD = V <sub>CC</sub> + 0.3V |                              |        | 1                            | μA    |

| CHOM Logic Input Throshold                        |                     | Logic high                                                             |                              |        | 2.0                          | V     |

| SHDN Logic Input Threshold                        |                     | Logic low                                                              | 0.8                          |        |                              | V     |

| SHDN Logic Input Current                          |                     | SHDN = V <sub>CC</sub> or GND                                          | -1                           |        | +1                           | μΑ    |

Note 1: Limits are 100% production tested at  $T_A = +25$ °C. Limits over the operating temperature range are guaranteed through correlation using statistical-quality-control (SQC) methods.

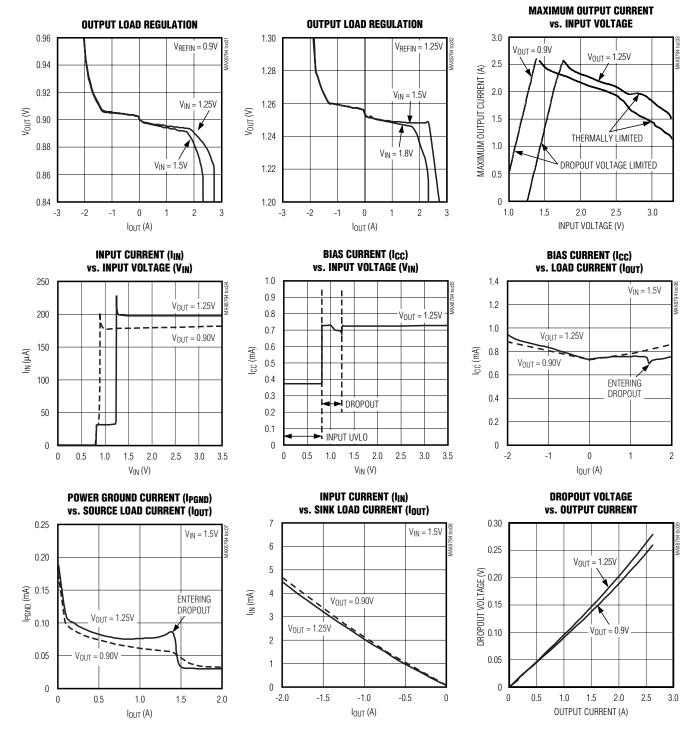

### Typical Operating Characteristics

(Circuit of Figure 1.  $T_A = +25$ °C, unless otherwise noted.)

## Typical Operating Characteristics (continued)

(Circuit of Figure 1.  $T_A = +25$ °C, unless otherwise noted.)

## Typical Operating Characteristics (continued)

(Circuit of Figure 1.  $T_A = +25$ °C, unless otherwise noted.)

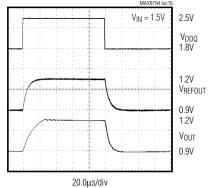

#### **DYNAMIC OUTPUT-VOLTAGE TRANSIENT**

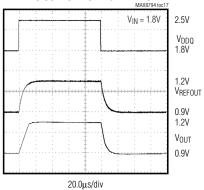

### DYNAMIC OUTPUT-VOLTAGE TRANSIENT

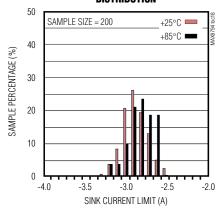

# SINK CURRENT-LIMIT DISTRIBUTION

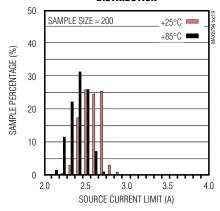

## SOURCE CURRENT-LIMIT DISTRIBUTION

## Pin Description

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                  |

|-----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | REFOUT          | Buffered Reference Output. The output of the unity-gain reference input buffer sources and sinks over 5mA. Bypass REFOUT to AGND with a 0.33µF or greater ceramic capacitor.                                                                                              |

| 2   | V <sub>CC</sub> | Analog Supply Input. Connect to the system supply voltage (+3.3V). Bypass V <sub>CC</sub> to AGND with a 1µF or greater ceramic capacitor.                                                                                                                                |

| 3   | AGND            | Analog Ground. Connect the backside pad to AGND.                                                                                                                                                                                                                          |

| 4   | REFIN           | External Reference Input. REFIN sets the output regulation voltage (V <sub>OUTS</sub> = V <sub>REFIN</sub> ).                                                                                                                                                             |

| 5   | PGOOD           | Open-Drain Power-Good Output. PGOOD is low when the output voltage is more than 150mV (typ) above or below the regulation point, during soft-start, and when shut down. 2ms after the output reaches the regulation voltage during startup, PGOOD becomes high impedance. |

| 6   | OUTS            | Output Sense Input. The OUTS regulation level is set by the voltage at REFIN. Connect OUTS to the remote DDR termination bypass capacitors. OUTS is internally connected to OUT through a $12k\Omega$ resistor.                                                           |

| 7   | SHDN            | Shutdown Control Input. Connect to V <sub>CC</sub> for normal operation. Connect to analog ground to shut down the linear regulator. The reference buffer remains active in shutdown.                                                                                     |

| 8   | PGND            | Power Ground. Internally connected to the output sink MOSFET.                                                                                                                                                                                                             |

| 9   | OUT             | Output of the Linear Regulator                                                                                                                                                                                                                                            |

| 10  | IN              | Power Input. Internally connected to the output source MOSFET.                                                                                                                                                                                                            |

### **Detailed Description**

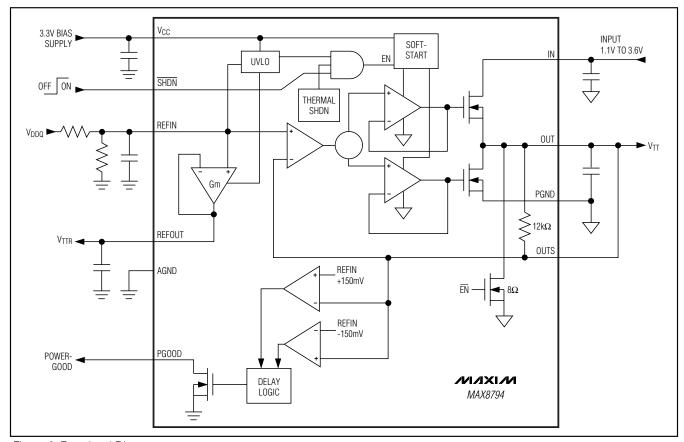

The MAX8794 is a low-voltage, low-dropout DDR termination linear regulator with an external bias supply input and a buffered reference output (see Figures 1 and 2). V<sub>CC</sub> is powered by a 2.7V to 3.6V supply that is commonly available in laptop and desktop computers. The 3.3V bias supply drives the gate of the internal pass transistor, while a lower voltage input at the drain of the transistor (IN) is regulated to provide V<sub>OUT</sub>. By using separate bias and power inputs, the MAX8794 can drive an n-channel high-side MOSFET and use a lower input voltage to provide better efficiency.

The MAX8794 regulates its output voltage to the voltage at REFIN. When used in DDR applications as a termination supply, the MAX8794 delivers 1.25V or 0.9V at 3A peak (typ) from an input voltage of 1.1V to 3.6V. The MAX8794 sinks up to 3A peak (typ) as required in a termination supply. The MAX8794 provides shoot-through protection, ensuring that the source and sink MOSFETs do not conduct at the same time, yet produces a fast source-to-sink load transient.

Figure 1. Standard Application Circuit

Figure 2. Functional Diagram

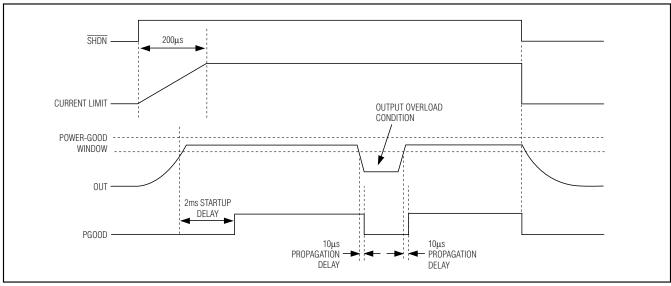

The MAX8794 features an open-drain PGOOD output that transitions high 2ms after the output initially reaches regulation. PGOOD goes low within 10µs of when the output goes out of regulation by ±150mV. The MAX8794 features current- and thermal-limiting circuitry to prevent damage during fault conditions.

### 3.3V Bias Supply (Vcc)

The V<sub>CC</sub> input powers the control circuitry and provides the gate drive to the pass transistor. This improves efficiency by allowing V<sub>IN</sub> to be powered from a lower supply voltage. Power V<sub>CC</sub> from a well-regulated 3.3V supply. Current drawn from the V<sub>CC</sub> supply remains relatively constant with variations in V<sub>IN</sub> and load current. Bypass V<sub>CC</sub> with a 1 $\mu$ F or greater ceramic capacitor as close to the device as possible.

### **Vcc Undervoltage Lockout (UVLO)**

The V<sub>CC</sub> input UVLO circuitry ensures that the regulator starts up with adequate voltage for the gate-drive circuitry to bias the internal pass transistor. The UVLO threshold is 2.55V (typ). V<sub>CC</sub> must remain above this level for proper operation.

### **Power-Supply Input (IN)**

IN provides the source current for the linear regulator's output, OUT. IN connects to the drain of the internal n-channel power MOSFET. IN can be as low as 1.1V, minimizing power dissipation. The input UVLO prohibits operation below 0.8V (typ). Bypass IN with a  $10\mu F$  or greater capacitor as close to the device as possible.

#### Reference Input (REFIN)

The MAX8794 regulates OUTS to the voltage set at REFIN, making the MAX8794 ideal for memory applications where the termination supply must track the supply voltage. Typically, REFIN is set by an external resistive voltage-divider connected to the memory supply (VDDQ) as shown in Figure 1.

The maximum output voltage of 1.5V is limited by the gate-drive voltage of the internal n-channel power transistor.

### **Buffered Reference Output (REFOUT)**

REFOUT is a unity-gain transconductance amplifier that generates the DDR reference supply. It sources and sinks greater than 5mA. The reference buffer is typically

connected to ceramic bypass capacitors (0.33 $\mu$ F to 1.0 $\mu$ F). REFOUT is active when V<sub>REFIN</sub> > 0.45V and V<sub>CC</sub> is above V<sub>UVLO</sub>. REFOUT is independent of SHDN.

#### **Shutdown**

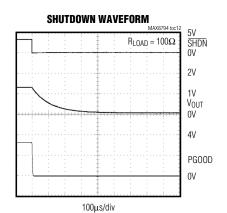

Drive  $\overline{SHDN}$  low to disable the error amplifier, gatedrive circuitry, and pass transistor (Figure 2). In shutdown, OUT is terminated to GND with an  $8\Omega$  MOSFET. REFOUT is independent of  $\overline{SHDN}$ . Connect  $\overline{SHDN}$  to VCC for normal operation.

### **Current Limit**

The MAX8794 features source and sink current limits to protect the internal n-channel MOSFETs. The source-and-sink MOSFETs have a typical 3A current limit (1.8A min). This current limit prevents damage to the internal power transistors, but the device can enter thermal shutdown if the power dissipation increases the die temperature above +165°C (see the *Thermal-Overload Protection* section).

### **Soft-Start Current Limit**

Soft-start gradually increases the internal source current limit to reduce input surge currents at startup. Full-source current limit is available after the 200µs soft-start timer has expired. The soft-start current limit is given by:

$$I_{\text{LIMIT(SS)}} = \frac{I_{\text{LIMIT}} \times t}{t_{\text{SS}}}$$

where I<sub>LIMIT</sub> and tss are from the *Electrical Characteristics*. Figure 3 shows the MAX8794 PGOOD and soft-start waveform.

#### **Thermal-Overload Protection**

Thermal-overload protection prevents the linear regulator from overheating. When the junction temperature exceeds +165°C, the linear regulator and reference buffer are disabled, allowing the device to cool. Normal operation resumes once the junction temperature cools by 15°C. Continuous short-circuit conditions result in a pulsed output until the overload is removed. A continuous thermal-overload condition results in a pulsed output. For continuous operation, do not exceed the absolute maximum junction-temperature rating of +150°C.

Figure 3. MAX8794 PGOOD and Soft-Start Waveforms

### **Power-Good (PGOOD)**

The MAX8794 provides an open-drain PGOOD output that goes high 2ms (typ) after the output initially reaches regulation during startup. PGOOD transitions low 10µs after the output goes out of regulation by  $\pm 150$ mV, or when the device enters shutdown. Connect a pullup resistor from PGOOD to VCC for a logic-level output. Use a 100k $\Omega$  resistor to minimize current consumption.

## Applications Information

### **Dynamic Output-Voltage Transitions**

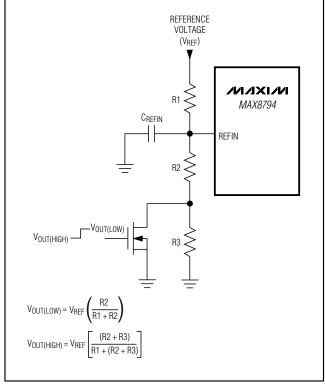

By changing the voltage at REFIN, the MAX8794 can be used in applications that require dynamic output-voltage changes between two set points (graphics processors). Figure 4 shows a dynamically adjustable resistive voltage-divider network at REFIN. Using an external signal MOSFET, a resistor can be switched in and out of the REFIN resistor-divider, changing the voltage at REFIN. The two output voltages are determined by the following equations:

$$V_{OUT(LOW)} = V_{REF} \left( \frac{R2}{R1 + R2} \right)$$

$$V_{OUT(HIGH)} = V_{REF} \left[ \frac{(R2 + R3)}{R1 + (R2 + R3)} \right]$$

Figure 4. Dynamic Output-Voltage Change

For a step-voltage change at REFIN, the rate of change of the output voltage is limited by the total output capacitance, the current limit, and the load during the transition. Adding a capacitor across REFIN and AGND filters noise and controls the rate of change of the REFIN voltage during dynamic transitions. With the additional capacitance, the REFIN voltage slews between the two set points with a time constant given by REQ x CREFIN, where REQ is the equivalent parallel resistance seen by the slew capacitor.

### **Operating Region and Power Dissipation**

The maximum power dissipation of the MAX8794 depends on the thermal resistance of the 10-pin TDFN package and the circuit board, the temperature difference between the die and ambient air, and the rate of airflow. The power dissipated in the device is:

The resulting maximum power dissipation is:

$$P_{DIS(MAX)} = \frac{T_{J(MAX)} - T_{A}}{\theta_{JC} + \theta_{CA}}$$

where  $T_{J(MAX)}$  is the maximum junction temperature (+150°C),  $T_A$  is the ambient temperature,  $\theta_{JC}$  is the thermal resistance from the die junction to the package case, and  $\theta_{CA}$  is the thermal resistance from the case through the PC board, copper traces, and other materials to the surrounding air. For optimum power dissipation, use a large ground plane with good thermal contact to the backside pad, and use wide input and output traces.

When  $1\text{in}^2$  of copper is connected to the device, the maximum allowable power dissipation of a 10-pin TDFN package is 1951mW. The maximum power dissipation is derated by 24.4mW/°C above  $T_A = +70^{\circ}\text{C}$ . Extra copper on the PC board increases thermal mass and reduces thermal resistance of the board. Refer to the MAX8794 evaluation kit for a layout example.

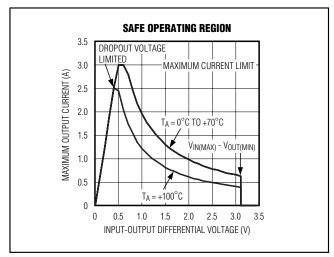

The MAX8794 delivers up to 3A and operates with input voltages up to 3.6V, but not simultaneously. High output currents can only be achieved when the input-output differential voltages are low (Figure 5).

#### **Dropout Operation**

A regulator's minimum input-to-output voltage differential (dropout voltage) determines the lowest usable supply voltage. Because the MAX8794 uses an n-channel pass transistor, the dropout voltage is a function of the drain-to-source on-resistance (RDS(ON) =  $0.25\Omega$  max) multiplied by the load current (see the *Typical Operating Characteristics*):

Figure 5. Power Operating Region—Maximum Output Current vs. Input-Output Differential Voltage

VDROPOUT = RDS(ON) X IOUT

For low output-voltage applications, the sink current is limited by the output voltage and the R<sub>DS(ON)</sub> of the MOSFET.

### **Input Capacitor Selection**

Bypass IN to PGND with a  $10\mu\text{F}$  or greater ceramic capacitor. Bypass V<sub>CC</sub> to AGND with a  $1\mu\text{F}$  ceramic capacitor for normal operation in most applications. Typically, the LDO is powered from the output of a step-down controller (memory supply) that has additional bulk capacitance (polymer or tantalum) and distributed ceramic capacitors.

#### **Output Capacitor Selection**

The MAX8794 output stability is independent of the output capacitance for  $C_{OUT}$  from  $10\mu F$  to  $220\mu F$ . Capacitor ESR between  $2m\Omega$  and  $50m\Omega$  is needed to maintain stability. Within the recommended capacitance and ESR limits, the output capacitor should be chosen to provide good transient response:

$$\Delta I_{OUT(P-P)} \times ESR = \Delta V_{OUT(P-P)}$$

where  $\Delta I_{OUT(P-P)}$  is the maximum peak-to-peak load-current step (typically equal to the maximum source load plus the maximum sink load), and  $\Delta V_{OUT(P-P)}$  is the allowable peak-to-peak voltage tolerance.

Using larger output capacitance can improve efficiency in applications where the source and sink currents change rapidly. The capacitor acts as a reservoir for the rapid source and sink currents, so no extra current is supplied by the MAX8794 or discharged to ground, improving efficiency.

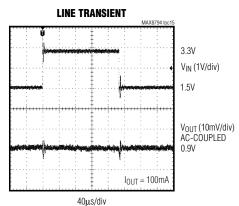

### Noise, PSRR, and Transient Response

The MAX8794 operates with low-dropout voltage and low quiescent current in notebook computers while maintaining good noise, transient response, and AC-rejection specifications. Improved supply-noise rejection and transient response can be achieved by increasing the values of the input and output capacitors. Use passive filtering techniques when operating from noisy sources.

The MAX8794 load-transient response graphs (see the *Typical Operating Characteristics*) show two components of the output response: a DC shift from the output impedance due to the load-current change and the transient response. A typical transient response for a step change in the load current from -1.5A to +1.5A is 10mV. Increasing the output capacitor's value and decreasing the ESR attenuate the overshoot.

### **PC Board Layout Guidelines**

The MAX8794 requires proper layout to achieve the intended output power level and low noise. Proper layout involves the use of a ground plane, appropriate component placement, and correct routing of traces using appropriate trace widths. Refer to the MAX8794 evaluation kit for a layout example:

- 1) Minimize high-current ground loops. Connect the ground of the device, the input capacitor, and the output capacitor together at one point.

- 2) To optimize performance, a ground plane is essential. Use all available copper layers in applications where the device is located on a multilayer board.

- 3) Connect the input filter capacitor less than 10mm from IN. The connecting copper trace carries large currents and must be at least 2mm wide, preferably 5mm wide.

- 4) Connect the backside pad to a large ground plane. Use as much copper as necessary to decrease the thermal resistance of the device. In general, more copper provides better heatsinking capabilities.

\_Chip Information

TRANSISTOR COUNT: 3496

PROCESS: BICMOS

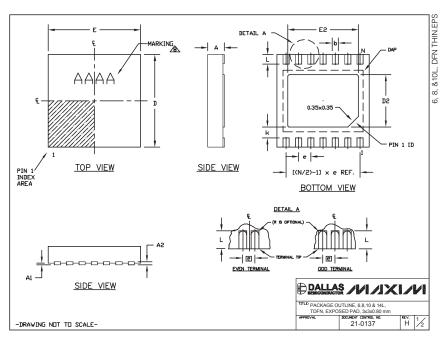

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

| COMMON D                                                               | DIMEN                                                | SIONS                                     |                                                           | PACKAGE V  | ARIAT                      | IONS                                |            |          |                         |           |               |

|------------------------------------------------------------------------|------------------------------------------------------|-------------------------------------------|-----------------------------------------------------------|------------|----------------------------|-------------------------------------|------------|----------|-------------------------|-----------|---------------|

| SYMBOL I                                                               | MIN.                                                 | MAX.                                      |                                                           | PKG. CODE  | N                          | D2                                  | E2         | е        | JEDEC SPEC              | b         | [(N/2)-1] x e |

| Α (                                                                    | 0.70                                                 | 0.80                                      |                                                           | T633-1     | 6                          | 1.50±0.10                           | 2.30±0.10  | 0.95 BSC | MO229 / WEEA            | 0.40±0.05 | 1.90 REF      |

| D :                                                                    | 2.90                                                 | 3.10                                      |                                                           | T633-2     | 6                          | 1.50±0.10                           | 2.30±0.10  | 0.95 BSC | MO229 / WEEA            | 0.40±0.05 | 1.90 REF      |

| E :                                                                    | 2.90                                                 | 3.10                                      |                                                           | T833-1     | 8                          | 1.50±0.10                           | 2.30±0.10  | 0.65 BSC | MO229 / WEEC            | 0.30±0.05 | 1.95 REF      |

| A1 (                                                                   | 0.00                                                 | 0.05                                      |                                                           | T833-2     | 8                          | 1.50±0.10                           | 2.30±0.10  | 0.65 BSC | MO229 / WEEC            | 0.30±0.05 | 1.95 REF      |

| L (                                                                    | 0.20                                                 | 0.40                                      |                                                           | T833-3     | 8                          | 1.50±0.10                           | 2.30±0.10  | 0.65 BSC | MO229 / WEEC            | 0.30±0.05 | 1.95 REF      |

| k                                                                      | 0.25                                                 | MIN.                                      |                                                           | T1033-1    | 10                         | 1.50±0.10                           | 2.30±0.10  | 0.50 BSC | MO229 / WEED-3          | 0.25±0.05 | 2.00 REF      |

| A2                                                                     | 0.20                                                 | REF.                                      |                                                           | T1033-2    | 10                         | 1.50±0.10                           | 2.30±0.10  | 0.50 BSC | MO229 / WEED-3          | 0.25±0.05 | 2.00 REF      |

|                                                                        |                                                      |                                           |                                                           | T1433-1    | 14                         | 1.70±0.10                           | 2.30±0.10  | 0.40 BSC |                         | 0.20±0.05 | 2.40 REF      |

|                                                                        |                                                      |                                           |                                                           | T1433-2    | 14                         | 1.70±0.10                           | 2.30±0.10  | 0.40 BSC |                         | 0.20±0.05 | 2.40 REF      |

| NOTES:                                                                 | 4ENIC!/                                              | DAIC ADI                                  | . IN                                                      | ANICLES IN | DECE                       | orre                                |            |          |                         |           |               |

| 1. ALL DIN 2. COPLAN 3. WARPAG 4. PACKAG 5. DRAWIN 6. "N" IS 7. NUMBER | NARITY<br>GE SH<br>GE LEI<br>IG COI<br>THE 1<br>R OF | SHALL ALL NO NGTH/PA NFORMS TOTAL N LEADS | NOT EXC<br>T EXCEE<br>ACKAGE TO JED<br>UMBER (<br>SHOWN ) |            | m.<br>NSID<br>XCEP<br>EREN | ERED AS S<br>T DIMENSIO<br>CE ONLY. | NS "D2" AN |          | C(S).<br>ND T1433-1 & T | 1433–2.   |               |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.